# TMS320TCI648x Serial RapidIO (SRIO)

# **User's Guide**

Literature Number: SPRUE13A September 2006

| Pref | ace     |                                                                                         | 14 |

|------|---------|-----------------------------------------------------------------------------------------|----|

| 1    | Overvi  | ew                                                                                      | 16 |

|      | 1.1     | General RapidIO System                                                                  | 10 |

|      | 1.2     | RapidIO Feature Support in SRIO                                                         | 1  |

|      | 1.3     | Standards                                                                               | 2( |

|      | 1.4     | External Devices Requirements                                                           | 2( |

|      | 1.5     | TI Devices Supported By This Document                                                   | 2( |

| 2    | SRIO F  | Functional Description                                                                  | 2′ |

|      | 2.1     | Overview                                                                                | 2  |

|      | 2.2     | SRIO Pins                                                                               | 2  |

|      | 2.3     | Functional Operation                                                                    | 26 |

| 3    | Logica  | I/Transport Error Handling and Logging                                                  | 83 |

| 4    | Interru | pt Conditions                                                                           | 8  |

|      | 4.1     | CPU Interrupts                                                                          | 8  |

|      | 4.2     | General Description                                                                     | 8  |

|      | 4.3     | Interrupt Condition Status and Clear Registers                                          | 8  |

|      | 4.4     | Interrupt Condition Routing Registers                                                   | 9: |

|      | 4.5     | Interrupt Status Decode Registers                                                       | 9  |

|      | 4.6     | Interrupt Generation                                                                    | 9  |

|      | 4.7     | Interrupt Pacing                                                                        | 9  |

|      | 4.8     | Interrupt Handling 1                                                                    | 0  |

| 5    | SRIO F  | Registers 1                                                                             | 02 |

|      | 5.1     | Introduction 1                                                                          | 02 |

|      | 5.2     | Peripheral Identification Register (PID) 1                                              | 1  |

|      | 5.3     | Peripheral Control Register (PCR) 1                                                     | 1: |

|      | 5.4     | Peripheral Settings Control Register (PER_SET_CNTL) 1                                   | 1: |

|      | 5.5     | Peripheral Global Enable Register (GBL_EN) 1                                            |    |

|      | 5.6     | Peripheral Global Enable Status Register (GBL_EN_STAT) 1                                | 1  |

|      | 5.7     | Block <i>n</i> Enable Register (BLK <i>n</i> _EN) 1                                     | 19 |

|      | 5.8     | Block <i>n</i> Enable Status Register (BLK <i>n</i> _EN_STAT) 1                         | 2  |

|      | 5.9     | RapidIO DEVICEID1 Register (DEVICEID_REG1) 1                                            | 2  |

|      | 5.10    | RapidIO DEVICEID2 Register (DEVICEID_REG2) 1                                            |    |

|      | 5.11    | Packet Forwarding Register <i>n</i> for 16-Bit Device IDs (PF_16B_CNTL <i>n</i> ) 1     | 2  |

|      | 5.12    | Packet Forwarding Register <i>n</i> for 8-Bit Device IDs (PF_8B_CNTL <i>n</i> ) 1       |    |

|      | 5.13    | SERDES Receive Channel Configuration Register <i>n</i> (SERDES_CFGRX <i>n</i> _CNTL) 1  | 2  |

|      | 5.14    | SERDES Transmit Channel Configuration Register <i>n</i> (SERDES_CFGTX <i>n</i> _CNTL) 1 | 2  |

|      | 5.15    | SERDES Macro Configuration Register n (SERDES_CFGn_CNTL) 1                              | 3( |

|      | 5.16    | DOORBELLn Interrupt Condition Status Register (DOORBELLn_ICSR) 1                        | 32 |

|      | 5.17    | DOORBELLn Interrupt Condition Clear Register (DOORBELLn_ICCR) 1                         | 3  |

|      | 5.18    | RX CPPI Interrupt Status Register (RX_CPPI_ICSR) 1                                      | 3  |

|      | 5.19    | RX CPPI Interrupt Clear Register (RX_CPPI_ICCR) 1                                       | 3  |

|      | 5.20    | TX CPPI Interrupt Status Register (TX_CPPI_ICSR) 1                                      | 36 |

|      | 5.21    | TX CPPI Interrupt Clear Register (TX_CPPI_ICCR) 1                                       |    |

|      | 5.22    | LSU Interrupt Condition Status Register (LSU_ICSR) 1                                    | 38 |

| 5.23 | LSU Interrupt Condition Clear Register (LSU_ICCR)                                                                                     | 141 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.24 | Error, Reset, and Special Event Interrupt Condition Status Register<br>(ERR_RST_EVNT_ICSR)                                            | 142 |

| 5.25 | Error, Reset, and Special Event Interrupt Condition Clear Register<br>(ERR_RST_EVNT_ICCR)                                             | 143 |

| 5.26 | DOORBELL <i>n</i> Interrupt Condition Routing Registers (DOORBELL <i>n</i> _ICRR and DOORBELL <i>n</i> _ICRR2)                        | 144 |

| 5.27 | RX CPPI Interrupt Condition Routing Registers (RX_CPPI_ICRR and RX_CPPI_ICRR2)                                                        | 145 |

| 5.28 | TX CPPI Interrupt Condition Routing Registers (TX_CPPI_ICRR and TX_CPPI_ICRR2)                                                        | 146 |

| 5.29 | LSU Interrupt Condition Routing Registers (LSU_ICRR0–LSU_ICRR3)                                                                       | 147 |

| 5.30 | Error, Reset, and Special Event Interrupt Condition Routing Registers (ERR_RST_EVNT_ICRR, ERR_RST_EVNT_ICRR2, and ERR_RST_EVNT_ICRR3) | 149 |

| 5.31 | Interrupt Status Decode Register (INTDSTn_DECODE)                                                                                     |     |

| 5.32 | INTDST <i>n</i> Interrupt Rate Control Register (INTDST <i>n</i> _RATE_CNTL)                                                          | 154 |

| 5.33 | LSUn Control Register 0 (LSUn_REG0)                                                                                                   | 155 |

| 5.34 | LSUn Control Register 1 (LSUn_REG1)                                                                                                   | 156 |

| 5.35 | LSUn Control Register 2 (LSUn_REG2)                                                                                                   | 157 |

| 5.36 | LSUn Control Register 3 (LSUn_REG3)                                                                                                   |     |

| 5.37 | LSUn Control Register 4 (LSUn_REG4)                                                                                                   |     |

| 5.38 | LSUn Control Register 5 (LSUn_REG5)                                                                                                   |     |

| 5.39 | LSUn Control Register 6 (LSUn_REG6)                                                                                                   | 161 |

| 5.40 | LSU <i>n</i> Congestion Control Flow Mask Register (LSU <i>n</i> _FLOW_MASKS)                                                         |     |

| 5.41 | Queue <i>n</i> Transmit DMA Head Descriptor Pointer Register (QUEUE <i>n</i> _TXDMA_HDP)                                              |     |

| 5.42 | Queue <i>n</i> Transmit DMA Completion Pointer Register (QUEUE <i>n</i> _TXDMA_CP)                                                    | 165 |

| 5.43 | Queue <i>n</i> Receive DMA Head Descriptor Pointer Register (QUEUE <i>n</i> _RXDMA_HDP)                                               | 166 |

| 5.44 | Queue <i>n</i> Receive DMA Completion Pointer Register (QUEUE <i>n</i> _RXDMA_CP)                                                     | 167 |

| 5.45 | Transmit Queue Teardown Register (TX_QUEUE_TEAR_DOWN)                                                                                 |     |

| 5.46 | Transmit CPPI Supported Flow Mask Registers (TX_CPPI_FLOW_MASKS[0-7])                                                                 |     |

| 5.47 | Receive Queue Teardown Register (RX_QUEUE_TEAR_DOWN)                                                                                  |     |

| 5.48 | Receive CPPI Control Register (RX_CPPI_CNTL)                                                                                          |     |

| 5.49 | Transmit CPPI Weighted Round Robin Control Registers (TX_QUEUE_CNTL[0-3])                                                             |     |

| 5.50 | Mailbox to Queue Mapping Registers (RXU_MAP_Ln and RXU_MAP_Hn)                                                                        |     |

| 5.51 | Flow Control Table Entry Register n (FLOW_CNTLn)                                                                                      |     |

| 5.52 | Device Identity CAR (DEV_ID)                                                                                                          |     |

| 5.53 | Device Information CAR (DEV_INFO)                                                                                                     |     |

| 5.54 | Assembly Identity CAR (ASBLY_ID)                                                                                                      |     |

| 5.55 | Assembly Information CAR (ASBLY_INFO)                                                                                                 |     |

| 5.56 | Processing Element Features CAR (PE_FEAT)                                                                                             |     |

| 5.57 | Source Operations CAR (SRC_OP)                                                                                                        |     |

| 5.58 | Destination Operations CAR (DEST_OP)                                                                                                  |     |

| 5.59 | Processing Element Logical Layer Control CSR (PE_LL_CTL)                                                                              |     |

| 5.60 | Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR)                                                                           |     |

| 5.61 | Local Configuration Space Base Address 1 CSR (LCL_CFG_BAR)                                                                            |     |

| 5.62 | Base Device ID CSR (BASE_ID)                                                                                                          |     |

| 5.63 | Host Base Device ID Lock CSR (HOST_BASE_ID_LOCK)                                                                                      |     |

| 5.64 | Component Tag CSR (COMP_TAG)                                                                                                          |     |

| 5.65 | 1x/4x LP Serial Port Maintenance Block Header Register (SP_MB_HEAD)                                                                   |     |

| 5.66 | Port Link Time-Out Control CSR (SP_LT_CTL)                                                                                            |     |

| 5.67 | Port Response Time-Out Control CSR (SP_RT_CTL)                                                                                        |     |

| 5.68 | Port General Control CSR (SP_GEN_CTL)                                                                                                 | 199 |

|       | 5.69 | Port Link Maintenance Request CSR n (SPn_LM_REQ)                                          | 200 |

|-------|------|-------------------------------------------------------------------------------------------|-----|

|       | 5.70 | Port Link Maintenance Response CSR n (SPn_LM_RESP)                                        | 201 |

|       | 5.71 | Port Local AckID Status CSR n (SPn_ACKID_STAT)                                            | 202 |

|       | 5.72 | Port Error and Status CSR n (SPn_ERR_STAT)                                                | 203 |

|       | 5.73 | Port Control CSR n (SPn_CTL)                                                              | 206 |

|       | 5.74 | Error Reporting Block Header Register (ERR_RPT_BH)                                        | 209 |

|       | 5.75 | Logical/Transport Layer Error Detect CSR (ERR_DET)                                        | 210 |

|       | 5.76 | Logical/Transport Layer Error Enable CSR (ERR_EN)                                         | 212 |

|       | 5.77 | Logical/Transport Layer High Address Capture CSR (H_ADDR_CAPT)                            | 214 |

|       | 5.78 | Logical/Transport Layer Address Capture CSR (ADDR_CAPT)                                   | 215 |

|       | 5.79 | Logical/Transport Layer Device ID Capture CSR (ID_CAPT)                                   | 216 |

|       | 5.80 | Logical/Transport Layer Control Capture CSR (CTRL_CAPT)                                   | 217 |

|       | 5.81 | Port-Write Target Device ID CSR (PW_TGT_ID)                                               | 218 |

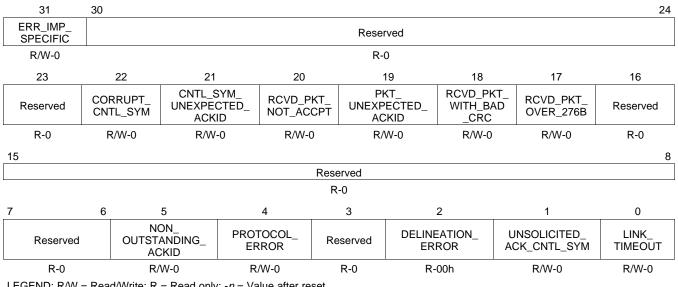

|       | 5.82 | Port Error Detect CSR <i>n</i> (SP <i>n</i> _ERR_DET)                                     | 219 |

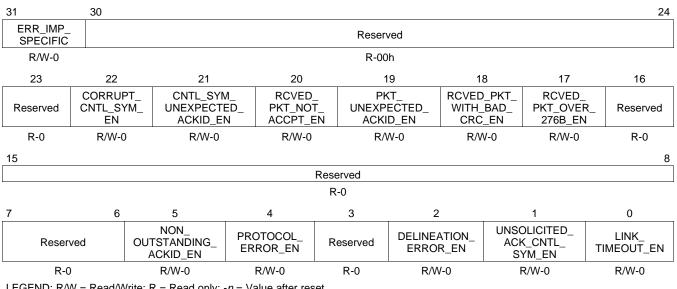

|       | 5.83 | Port Error Rate Enable CSR <i>n</i> (SP <i>n</i> _RATE_EN)                                | 221 |

|       | 5.84 | Port <i>n</i> Attributes Error Capture CSR 0 (SP <i>n</i> _ERR_ATTR_CAPT_DBG0)            | 223 |

|       | 5.85 | Port <i>n</i> Error Capture CSR 1 (SP <i>n</i> _ERR_CAPT_DBG1)                            | 224 |

|       | 5.86 | Port <i>n</i> Error Capture CSR 2 (SP <i>n</i> _ERR_CAPT_DBG2)                            | 225 |

|       | 5.87 | Port <i>n</i> Error Capture CSR 3 (SP <i>n</i> _ERR_CAPT_DBG3)                            | 226 |

|       | 5.88 | Port <i>n</i> Error Capture CSR 4 (SP <i>n</i> _ERR_CAPT_DBG4)                            | 227 |

|       | 5.89 | Port Error Rate CSR <i>n</i> (SP <i>n</i> _ERR_RATE)                                      | 228 |

|       | 5.90 | Port Error Rate Threshold CSR <i>n</i> (SP <i>n</i> _ERR_THRESH)                          | 229 |

|       | 5.91 | Port IP Discovery Timer for 4x Mode Register (SP_IP_DISCOVERY_TIMER)                      | 230 |

|       | 5.92 | Port IP Mode CSR (SP_IP_MODE)                                                             | 231 |

|       | 5.93 | Port IP Prescaler Register (IP_PRESCAL)                                                   | 233 |

|       | 5.94 | Port-Write-In Capture CSRs (SP_IP_PW_IN_CAPT[0–3])                                        | 234 |

|       | 5.95 | Port Reset Option CSR <i>n</i> (SP <i>n</i> _RST_OPT)                                     | 235 |

|       | 5.96 | Port Control Independent Register n (SPn_CTL_INDEP)                                       | 236 |

|       | 5.97 | Port Silence Timer <i>n</i> Register (SP <i>n</i> _SILENCE_TIMER)                         | 238 |

|       | 5.98 | Port Multicast-Event Control Symbol Request Register <i>n</i> (SP <i>n</i> _MULT_EVNT_CS) | 239 |

|       | 5.99 | Port Control Symbol Transmit <i>n</i> Register (SP <i>n</i> _CS_TX)                       | 240 |

| Index |      |                                                                                           | 241 |

|       |      |                                                                                           |     |

### List of Figures

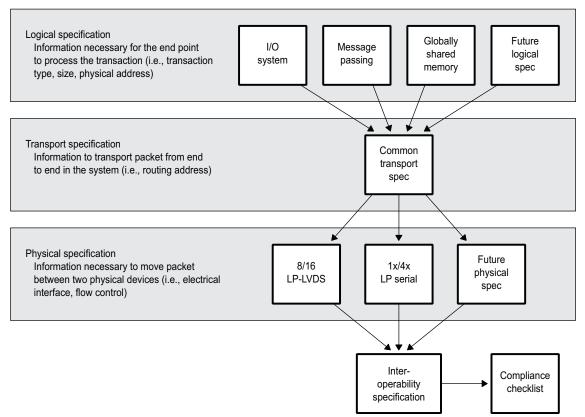

| 1  | RapidIO Architectural Hierarchy                                                                                          | 17 |

|----|--------------------------------------------------------------------------------------------------------------------------|----|

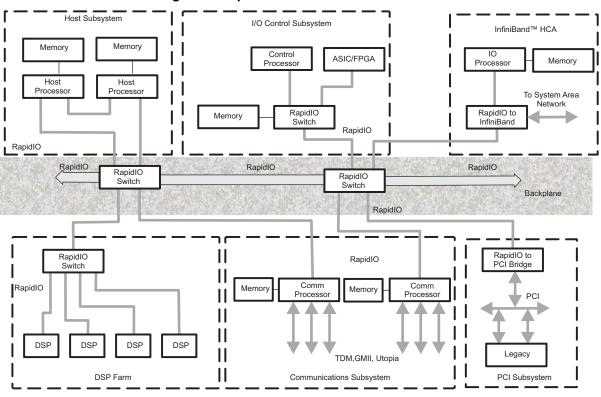

| 2  | RapidIO Interconnect Architecture                                                                                        | 18 |

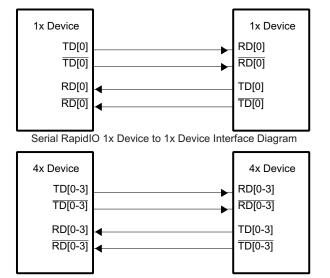

| 3  | Serial RapidIO Device to Device Interface Diagrams                                                                       | 19 |

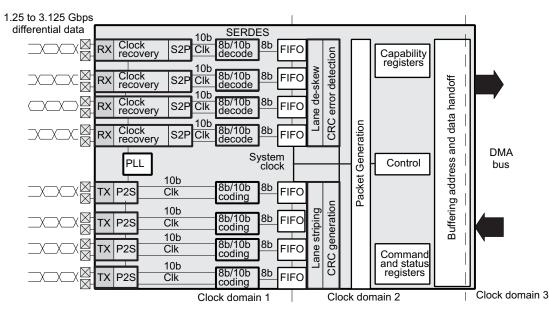

| 4  | SRIO Peripheral Block Diagram                                                                                            | 22 |

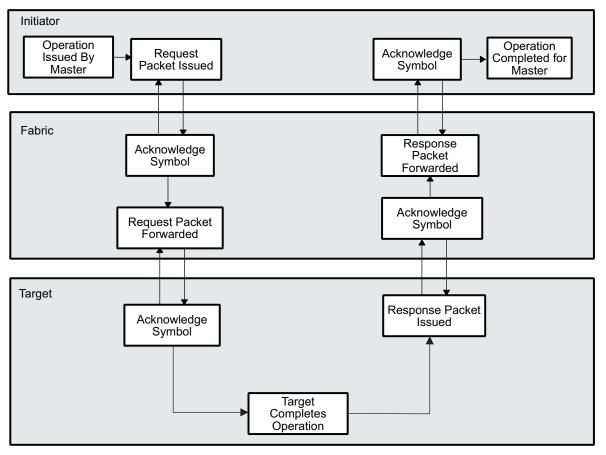

| 5  | Operation Sequence                                                                                                       | 23 |

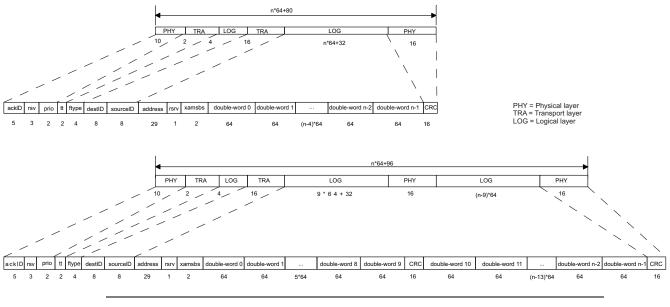

| 6  | 1x/4x RapidIO Packet Data Stream (Streaming-Write Class)                                                                 | 24 |

| 7  | Serial RapidIO Control Symbol Format                                                                                     | 24 |

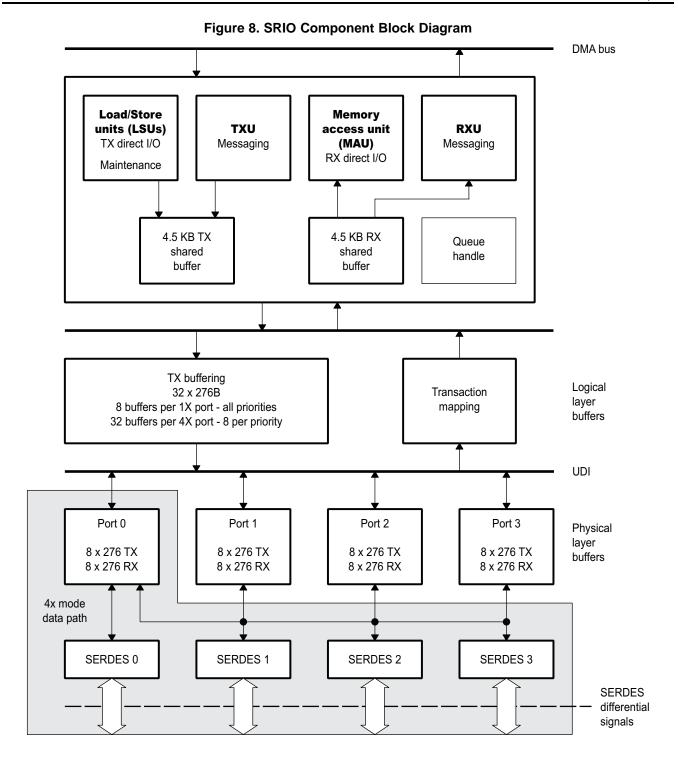

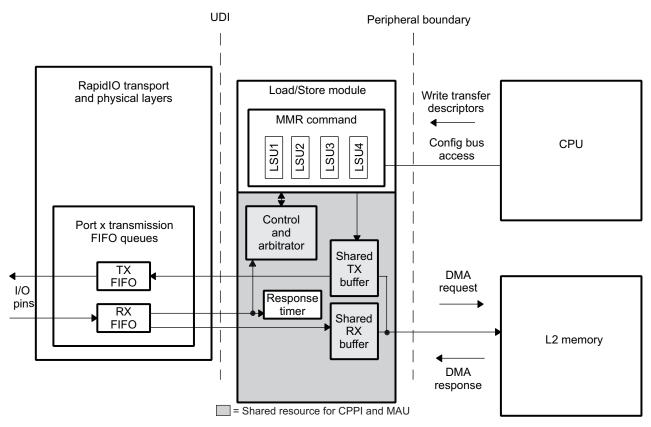

| 8  | SRIO Component Block Diagram                                                                                             | 27 |

| 9  | SERDES Macro Configuration Register 0 (SERDES_CFG0_CNTL)                                                                 | 28 |

| 10 | SERDES Receive Channel Configuration Register n (SERDES_CFGRXn_CNTL)                                                     | 31 |

| 11 | SERDES Transmit Channel Configuration Register <i>n</i> (SERDES_CFGTX <i>n</i> _CNTL)                                    | 33 |

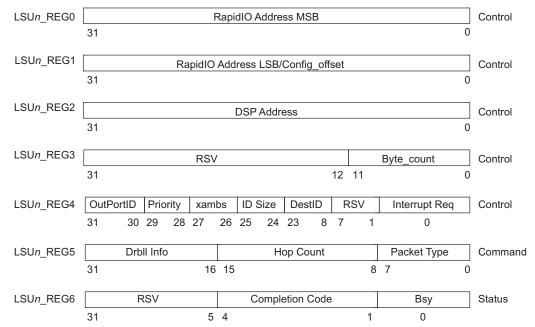

| 12 | Load/Store Registers for RapidIO (Address Offset: LSU1 400h–418h, LSU2 420h–438h, LSU3 440h–458h, LSU4 460h-478h)        | 36 |

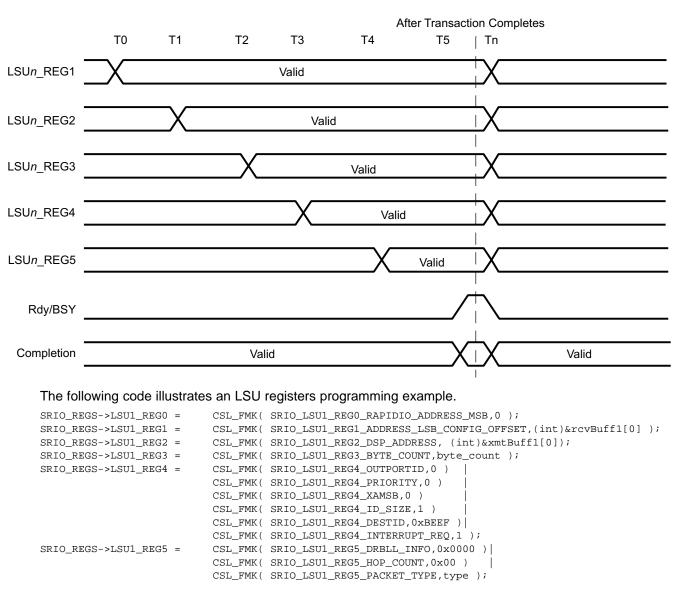

| 13 | LSU Registers Timing                                                                                                     | 38 |

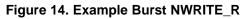

| 14 | Example Burst NWRITE_R                                                                                                   | 39 |

| 15 | Load/Store Module Data Flow Diagram                                                                                      | 40 |

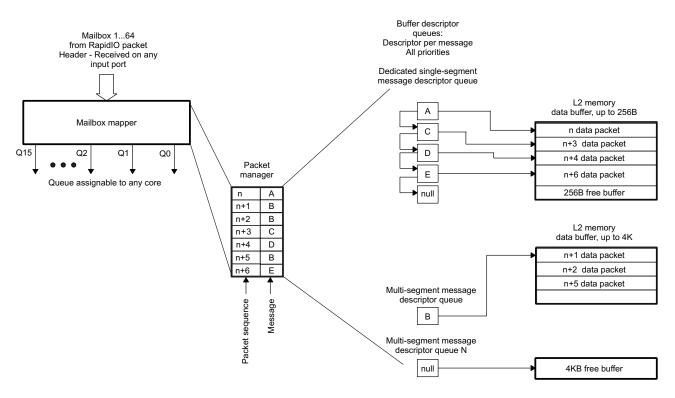

| 16 | CPPI RX Scheme for RapidIO                                                                                               | 44 |

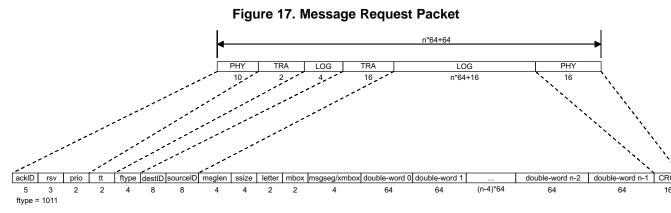

| 17 | Message Request Packet                                                                                                   | 45 |

| 18 | Mailbox to Queue Mapping Register Pair                                                                                   | 46 |

| 19 | RX Buffer Descriptor Fields                                                                                              | 47 |

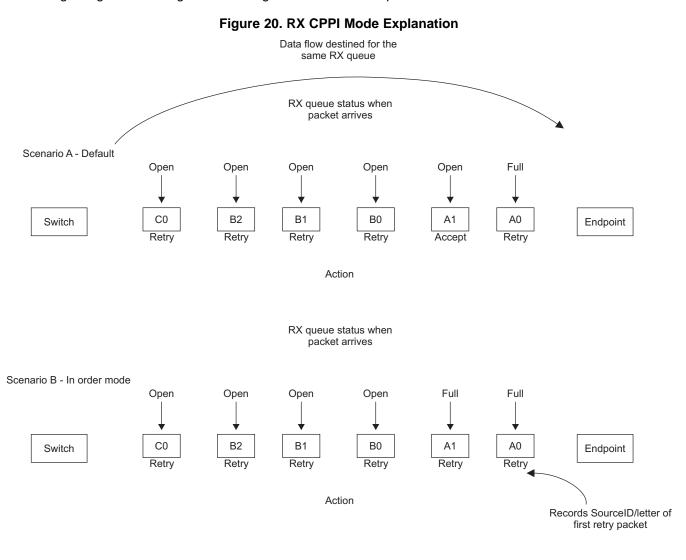

| 20 | RX CPPI Mode Explanation                                                                                                 | 49 |

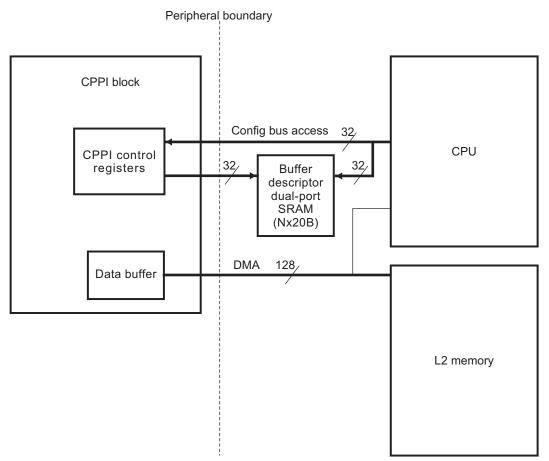

| 21 | CPPI Boundary Diagram                                                                                                    | 51 |

| 22 | TX Buffer Descriptor Fields                                                                                              | 52 |

| 23 | Weighted Round Robin Programming Registers (Address Offset 7E0h–7ECh)                                                    | 56 |

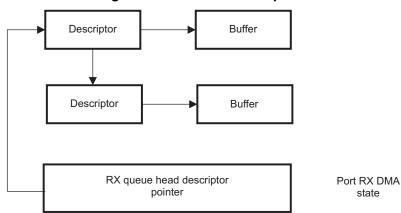

| 24 | RX Buffer Descriptors                                                                                                    | 62 |

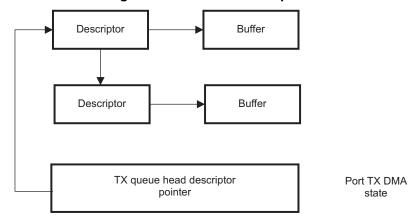

| 25 | TX Buffer Descriptors                                                                                                    | 63 |

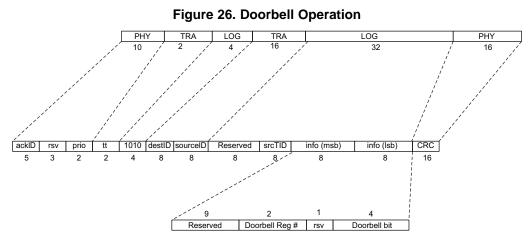

| 26 | Doorbell Operation                                                                                                       | 64 |

| 27 | Flow Control Table Entry Registers (Address Offset 0900h–093Ch)                                                          | 66 |

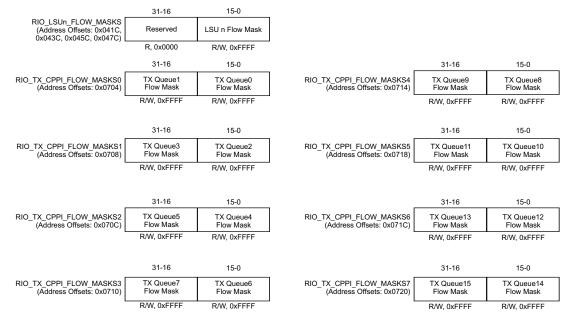

| 28 | Transmit Source Flow Control Masks                                                                                       | 67 |

| 29 | Fields Within Each Flow Mask                                                                                             | 67 |

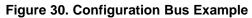

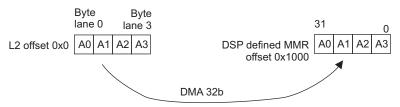

| 30 | Configuration Bus Example                                                                                                | 69 |

| 31 | DMA Example                                                                                                              | 69 |

| 32 | GBL_EN (Address 0030h)                                                                                                   | 71 |

| 33 | GBL_EN_STAT (Address 0034h)                                                                                              | 71 |

| 34 | BLK0_EN (Address 0038h)                                                                                                  | 72 |

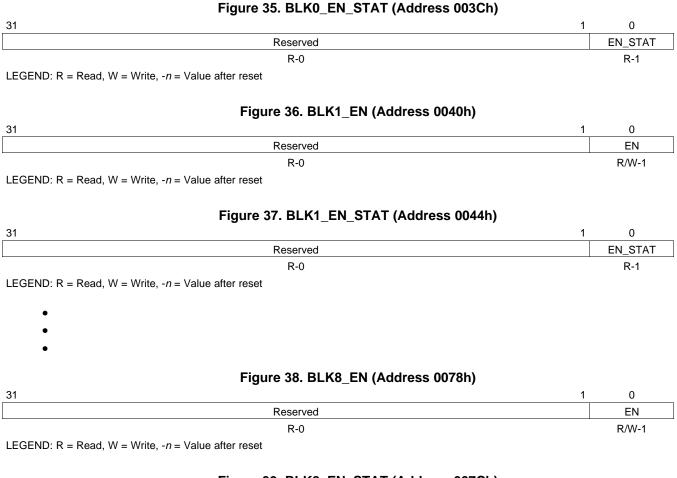

| 35 | BLK0_EN_STAT (Address 003Ch)                                                                                             | 73 |

| 36 | BLK1_EN (Address 0040h)                                                                                                  | 73 |

| 37 | BLK1_EN_STAT (Address 0044h)                                                                                             | 73 |

| 38 | BLK8_EN (Address 0078h)                                                                                                  | 73 |

| 39 | BLK8_EN_STAT (Address 007Ch)                                                                                             | 73 |

| 40 | Peripheral Control Register (PCR) - Address Offset 0004h                                                                 | 74 |

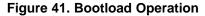

| 41 | Bootload Operation                                                                                                       | 80 |

| 42 | Packet Forwarding Register <i>n</i> for 16-Bit Device IDs (PF_16B_CNTL <i>n</i> ) Offsets 0x0090, 0x0098, 0x00A0, 0x00A8 | 81 |

| 43 | Packet Forwarding Register <i>n</i> for 8-Bit Device IDs (PF_8B_CNTL <i>n</i> ) Offsets 0x0094, 0x009C, 0x00A4, 0x00AC   | 82 |

| 44 | Logical/Transport Layer Error Detect CSR (ERR_DET)                                                                       | 83 |

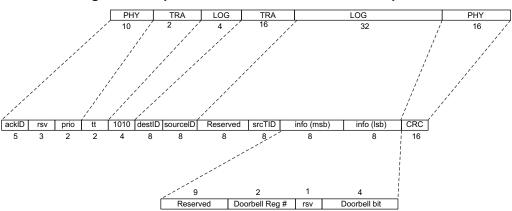

| 45 | RapidIO DOORBELL Packet for Interrupt Use                                                                                | 85 |

| 46 | Doorbell 0 Interrupt Condition Status and Clear Registers                                                                | 87 |

| 47 | Doorbell 1 Interrupt Condition Status and Clear Registers                                                                | 87 |

| 48 | Doorbell 2 Interrupt Condition Status and Clear Registers                                                                |    |

| 49 | Doorbell 3 Interrupt Condition Status and Clear Registers                                                                | 88 |

| 50       | RX CPPI Interrupt Condition Status and Clear Registers                                              | . 89 |

|----------|-----------------------------------------------------------------------------------------------------|------|

| 51       | TX CPPI Interrupt Condition Status and Clear Registers                                              | . 89 |

| 52       | LSU Interrupt Condition Status and Clear Registers                                                  | . 90 |

| 53       | Error, Reset, and Special Event Interrupt Condition Status and Clear Registers                      | . 91 |

| 54       | Doorbell 0 Interrupt Condition Routing Registers                                                    | . 94 |

| 55       | RX CPPI Interrupt Condition Routing Registers                                                       | . 94 |

| 56       | TX CPPI Interrupt Condition Routing Registers                                                       | . 95 |

| 57       | LSU Interrupt Condition Routing Registers                                                           | . 96 |

| 58       | Error, Reset, and Special Event Interrupt Condition Routing Registers                               | . 97 |

| 59       | Interrupt Status Decode Register (INTDSTn_DECODE)                                                   | . 98 |

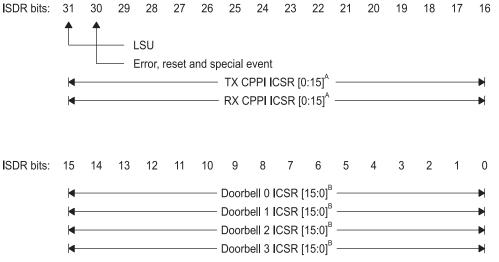

| 60       | Interrupt Sources Assigned to ISDR Bits                                                             | . 98 |

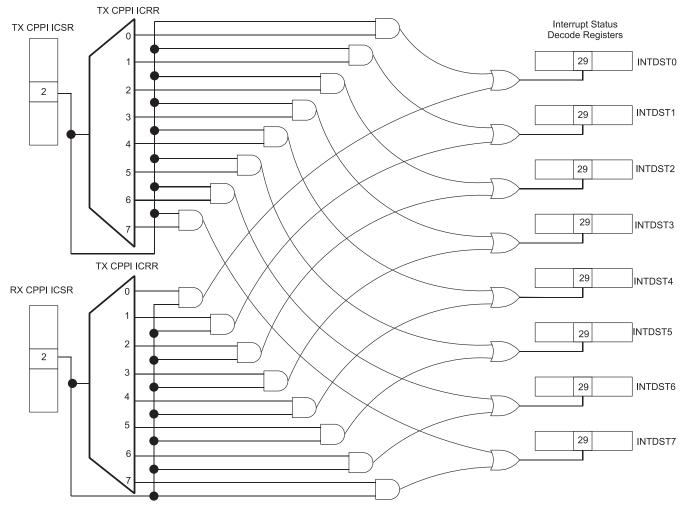

| 61       | Example Diagram of Interrupt Status Decode Register Mapping                                         | . 99 |

| 62       | INTDSTn_RATE_CNTL Interrupt Rate Control Register                                                   | 100  |

| 63       | Peripheral ID Register (PID) - Address Offset 0000h                                                 | 111  |

| 64       | Peripheral Control Register (PCR) - Address Offset 0004h                                            | 112  |

| 65       | Peripheral Settings Control Register (PER_SET_CNTL) (Address Offset 0020h)                          | 113  |

| 66       | Peripheral Global Enable Register (GBL_EN) (Address Offset 0030h)                                   |      |

| 67       | Peripheral Global Enable Status Register (GBL_EN_STAT) - Address 0034h                              | 117  |

| 68       | Block <i>n</i> Enable Register (BLK <i>n</i> _EN)                                                   | 119  |

| 69       | Block n Enable Status Register (BLKn_EN)                                                            | 120  |

| 70       | RapidIO DEVICEID1 Register (DEVICEID_REG1) (Offset 0080h)                                           | 121  |

| 71       | RapidIO DEVICEID2 Register (DEVICEID_REG2) (Offset 0x0084)                                          | 122  |

| 72       | Packet Forwarding Register <i>n</i> for 16-Bit Device IDs (PF_16B_CNTL <i>n</i> )                   | 123  |

| 73       | Packet Forwarding Register <i>n</i> for 8-Bit Device IDs (PF_8B_CNTL <i>n</i> )                     | 124  |

| 74       | SERDES Receive Channel Configuration Register <i>n</i> (SERDES_CFGRX <i>n</i> _CNTL)                | 125  |

| 75       | SERDES Transmit Channel Configuration Register <i>n</i> (SERDES_CFGTX <i>n</i> _CNTL)               | 128  |

| 76       | SERDES Macro Configuration Register n (SERDES_CFGn_CNTL)                                            | 130  |

| 77       | Doorbell <i>n</i> Interrupt Condition Status Register (DOORBELL <i>n</i> _ICSR)                     | 132  |

| 78       | Doorbell <i>n</i> Interrupt Condition Clear Register (DOORBELL <i>n</i> _ICCR)                      | 133  |

| 79       | RX CPPI Interrupt Condition Status Register (RX_CPPI_ICSR) - Address Offset 0240h                   | 134  |

| 80       | RX CPPI Interrupt Condition Clear Register (RX_CPPI_ICCR) - Address Offset 0248h                    | 135  |

| 81       | TX CPPI Interrupt Condition Status Register (TX_CPPI_ICSR) - Address Offset 0250h                   | 136  |

| 82       | TX CPPI Interrupt Condition Clear Register (TX_CPPI_ICCR) - Address Offset 0258h                    | 137  |

| 83       | LSU Interrupt Condition Status Register (LSU_ICSR) - Address Offset 0260h                           | 138  |

| 84       | LSU Interrupt Condition Clear Register (LSU_ICCR) - Address Offset 0268h                            | 141  |

| 85       | Error, Reset, and Special Event Interrupt Condition Status Register (ERR_RST_EVNT_ICSR) - Address   |      |

|          | Offset 0270h                                                                                        | 142  |

| 86       | Error, Reset, and Special Event Interrupt Condition Clear Register (ERR_RST_EVNT_ICCR) - Address    | 140  |

| 87       | Offset 0278h<br>Doorbell <i>n</i> Interrupt Condition Routing Registers                             |      |

| 88       |                                                                                                     |      |

| 89       | RX CPPI Interrupt Condition Routing Registers         TX CPPI Interrupt Condition Routing Registers |      |

| 89<br>90 | LSU Interrupt Condition Routing Registers                                                           |      |

| 90<br>91 | Error, Reset, and Special Event Interrupt Condition Routing Registers                               |      |

| 92       | Interrupt Status Decode Register (INTDST <i>n</i> _DECODE)                                          |      |

| 93       | INTDST <i>n</i> Interrupt Rate Control Register (INTDST <i>n</i> _RATE_CNTL)                        |      |

| 94       | LSU <i>n</i> Control Register 0 (LSU <i>n</i> _REG0)                                                |      |

| 95       | LSU <i>n</i> Control Register 0 (LSU <i>n</i> _REG1)                                                |      |

| 95<br>96 | LSU <i>n</i> Control Register 7 (LSU <i>n</i> _REG2)                                                |      |

| 90<br>97 | LSU <i>n</i> Control Register 2 (LSU <i>n</i> _REG2)                                                |      |

| 98       | LSU <i>n</i> Control Register 3 (LSU <i>n</i> _REG3)                                                |      |

| 99       | LSU <i>n</i> Control Register 5 (LSU <i>n</i> _REG5)                                                |      |

| 100      | LSU <i>n</i> Control Register 6 (LSU <i>n</i> _REG6)                                                |      |

| 101      | LSU <i>n</i> Congestion Control Flow Mask Register (LSU <i>n</i> _FLOW_MASKS)                       |      |

|          | J                                                                                                   |      |

| 102 | LSU <i>n</i> FLOW_MASK Fields                                                                | 162 |

|-----|----------------------------------------------------------------------------------------------|-----|

| 103 | Queue <i>n</i> Transmit DMA Head Descriptor Pointer Register (QUEUE <i>n</i> _TXDMA_HDP)     | 164 |

| 104 | Queue <i>n</i> Transmit DMA Completion Pointer Register (QUEUE <i>n</i> _TXDMA_CP)           | 165 |

| 105 | Queue <i>n</i> Receive DMA Head Descriptor Pointer Register (QUEUE <i>n</i> _RXDMA_HDP)      | 166 |

| 106 | Queue <i>n</i> Receive DMA Completion Pointer Register (QUEUE <i>n</i> _RXDMA_CP)            | 167 |

| 107 | Transmit Queue Teardown Register (TX_QUEUE_TEAR_DOWN) - Address Offset 0700h                 | 168 |

| 108 | Transmit CPPI Supported Flow Mask Registers                                                  | 170 |

| 109 | TX Queue <i>n</i> FLOW_MASK Fields                                                           | 170 |

| 110 | Receive Queue Teardown Register (RX_QUEUE_TEAR_DOWN) (Address Offset 0740h)                  | 172 |

| 111 | Receive CPPI Control Register (RX_CPPI_CNTL) (Address Offset 0744h)                          | 173 |

| 112 | Transmit CPPI Weighted Round Robin Control Registers                                         | 174 |

| 113 | Mailbox to Queue Mapping Register Pair                                                       |     |

| 114 | Flow Control Table Entry Register <i>n</i> (FLOW_CNTL <i>n</i> )                             | 181 |

| 115 | Device Identity CAR (DEV_ID) - Address Offset 1000h                                          | 182 |

| 116 | Device Information CAR (DEV_INFO) - Address Offset 1004h                                     | 183 |

| 117 | Assembly Identity CAR (ASBLY_ID) - Address Offset 1008h                                      |     |

| 118 | Assembly Information CAR (ASBLY_INFO) - Address Offset 100Ch                                 |     |

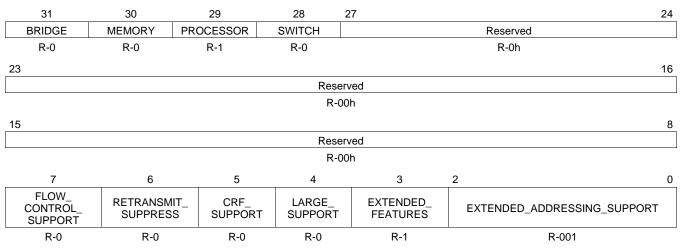

| 119 | Processing Element Features CAR (PE_FEAT) - Address Offset 1010h                             |     |

| 120 | Source Operations CAR (SRC_OP) - Address Offset 1018h                                        |     |

| 121 | Destination Operations CAR (DEST_OP) - Address Offset 101Ch                                  |     |

| 122 | Processing Element Logical Layer Control CSR (PE_LL_CTL) - Address Offset 104Ch              |     |

| 123 | Local Configuration Space Base Address 0 CSR (LCL_CFG_HBAR) - Address Offset 1058h           | 191 |

| 124 | Local Configuration Space Base Address 1 CSR (LCL_CFG_BAR) - Address Offset 105Ch            | 192 |

| 125 | Base Device ID CSR (BASE_ID) - Address Offset 1060h                                          | 193 |

| 126 | Host Base Device ID Lock CSR (HOST_BASE_ID_LOCK) - Address Offset 1068h                      |     |

| 127 | Component Tag CSR (COMP_TAG) - Address Offset 106Ch                                          | 195 |

| 128 | 1x/4x LP_Serial Port Maintenance Block Header Register (SP_MB_HEAD) - Address Offset 1100h   |     |

| 129 | Port Link Time-Out Control CSR (SP_LT_CTL) - Address Offset 1120h                            |     |

| 130 | Port Response Time-Out Control CSR (SP_RT_CTL) - Address Offset 1124h                        |     |

| 131 | Port General Control CSR (SP_GEN_CTL) - Address Offset 113Ch                                 |     |

| 132 | Port Link Maintenance Request CSR n (SPn_LM_REQ)                                             | 200 |

| 133 | Port Link Maintenance Response CSR n (SPn_LM_RESP)                                           | 201 |

| 134 | Port Local AckID Status CSR n (SPn_ACKID_STAT)                                               | 202 |

| 135 | Port Error and Status CSR n (SPn_ERR_STAT)                                                   | 203 |

| 136 | Port Control CSR n (SPn_CTL)                                                                 | 206 |

| 137 | Error Reporting Block Header Register (ERR_RPT_BH) - Address Offset 2000h                    | 209 |

| 138 | Logical/Transport Layer Error Detect CSR (ERR_DET) - Address Offset 2008h                    | 210 |

| 139 | Logical/Transport Layer Error Enable CSR (ERR_EN) - Address Offset 200Ch                     | 212 |

| 140 | Logical/Transport Layer High Address Capture CSR (H_ADDR_CAPT) - Address Offset 2010h        | 214 |

| 141 | Logical/Transport Layer Address Capture CSR (ADDR_CAPT) - Address Offset 2014h               | 215 |

| 142 | Logical/Transport Layer Device ID Capture CSR (ID_CAPT) - Address Offset 2018h               | 216 |

| 143 | Logical/Transport Layer Control Capture CSR (CTRL_CAPT) - Address Offset 201Ch               | 217 |

| 144 | Port-Write Target Device ID CSR (PW_TGT_ID) - Address Offset 2028h                           | 218 |

| 145 | Port Error Detect CSR n (SPn_ERR_DET)                                                        |     |

| 146 | Port Error Rate Enable CSR <i>n</i> (SP <i>n</i> _RATE_EN)                                   | 221 |

| 147 | Port <i>n</i> Attributes Error Capture CSR 0 (SP <i>n</i> _ERR_ATTR_CAPT_DBG0)               | 223 |

| 148 | Port <i>n</i> Error Capture CSR 1 (SP <i>n</i> _ERR_CAPT_DBG1)                               |     |

| 149 | Port <i>n</i> Error Capture CSR 2 (SP <i>n</i> _ERR_CAPT_DBG2)                               |     |

| 150 | Port <i>n</i> Error Capture CSR 3 (SP <i>n</i> _ERR_CAPT_DBG3)                               |     |

| 151 | Port <i>n</i> Error Capture CSR 4 (SP <i>n</i> _ERR_CAPT_DBG4)                               |     |

| 152 | Port Error Rate CSR n (SPn_ERR_RATE)                                                         |     |

| 153 | Port Error Rate Threshold CSR n (SPn_ERR_THRESH)                                             | 229 |

| 154 | Port IP Discovery Timer for 4x Mode Register (SP_IP_DISCOVERY_TIMER) - Address Offset 12000h | 230 |

| 155 | Port IP Mode CSR (SP_IP_MODE) - Address Offset 12004h                     | 231 |

|-----|---------------------------------------------------------------------------|-----|

| 156 | Port IP Prescaler Register (IP_PRESCAL) - Address Offset 12008h           | 233 |

| 157 | Port-Write-In Capture CSRs                                                | 234 |

| 158 | Port Reset Option CSR n (SPn_RST_OPT)                                     | 235 |

| 159 | Port Control Independent Register n (SPn_CTL_INDEP)                       | 236 |

| 160 | Port Silence Timer <i>n</i> Register (SP <i>n</i> _SILENCE_TIMER)         | 238 |

| 161 | Port Multicast-Event Control Symbol Request Register n (SPn_MULT_EVNT_CS) | 239 |

| 162 | Port Control Symbol Transmit <i>n</i> Register (SP <i>n</i> _CS_TX)       | 240 |

#### List of Tables

| 1  | TI Devices Supported By This Document                                                                    | 20  |

|----|----------------------------------------------------------------------------------------------------------|-----|

| 2  | Registers Checked for Multicast DeviceID                                                                 | 21  |

| 3  | Packet Types                                                                                             | 25  |

| 4  | Pin Description                                                                                          | 26  |

| 5  | SERDES Macro Configuration Register 0 (SERDES_CFG0_CNTL) Field Descriptions                              | 29  |

| 6  | Line Rate versus PLL Output Clock Frequency                                                              | 30  |

| 7  | Effect of the RATE Bits                                                                                  | 30  |

| 8  | Frequency Range versus MPY Value                                                                         | 30  |

| 9  | SERDES Receive Channel Configuration Register <i>n</i> (SERDES_CFGRX <i>n</i> _CNTL) Field Descriptions  | 31  |

| 10 | EQ Bits                                                                                                  | 33  |

| 11 | SERDES Transmit Channel Configuration Register <i>n</i> (SERDES_CFGTX <i>n</i> _CNTL) Field Descriptions | 33  |

| 12 | DE Bits of SERDES_CFGTXn_CNTL                                                                            | 34  |

| 13 | SWING Bits of SERDES_CFGTXn_CNTL                                                                         | 35  |

| 14 | LSU Control/Command Register Fields                                                                      | 36  |

| 15 | LSU Status Register Fields                                                                               | 37  |

| 16 | RX DMA State Head Descriptor Pointer (HDP) (Address Offset 600h–63Ch)                                    | 46  |

| 17 | RX DMA State Completion Pointer (CP) (Address Offset 680h–6BCh)                                          | 46  |

| 18 | RX Buffer Descriptor Field Descriptions                                                                  | 47  |

| 19 | TX DMA State Head Descriptor Pointer (HDP) (Address Offset 500h–53Ch)                                    | 51  |

| 20 | TX DMA State Completion Pointer (CP) (Address Offset 58h–5BCh)                                           | 52  |

| 21 | TX Buffer Descriptor Field Definitions                                                                   | 52  |

| 22 | Weighted Round Robin Programming Registers (Address Offset 7E0h–7ECh)                                    | 56  |

| 23 | Examples of DOORBELL_INFO Designations (See Figure 26 )                                                  | 64  |

| 24 | Flow Control Table Entry Register <i>n</i> (FLOW_CNTL <i>n</i> ) Field Descriptions                      | 67  |

| 25 | Fields Within Each Flow Mask                                                                             | 68  |

| 26 | Reset Hierarchy                                                                                          | 70  |

| 27 | Global Enable and Global Enable Status Field Descriptions                                                | 72  |

| 28 | Block Enable and Block Enable Status Field Descriptions                                                  |     |

| 29 | Peripheral Control Register (PCR) Field Descriptions                                                     |     |

| 30 | Port Mode Register Settings                                                                              |     |

| 31 | Multicast DeviceID Operation                                                                             | 81  |

| 32 | Packet Forwarding Register <i>n</i> for 16-Bit DeviceIDs (PF_16B_CNTL <i>n</i> ) Field Descriptions      |     |

| 33 | Packet Forwarding Register <i>n</i> for 8-Bit DeviceIDs (PF_8B_CNTL <i>n</i> ) Field Descriptions        |     |

| 34 | Logical/Transport Layer Error Detect CSR (ERR_DET) Field Descriptions                                    |     |

| 35 | Interrupt Condition Status and Clear Bits                                                                |     |

| 36 | Interrupt Conditions Shown in LSU_ICSR and Cleared With LSU_ICCR                                         |     |

| 37 | Interrupt Conditions Shown in ERR_RST_EVNT_ICSR and Cleared With ERR_RST_EVNT_ICCR                       |     |

| 38 | Interrupt Clearing Sequence for Special Event Interrupts                                                 |     |

| 39 | Interrupt Condition Routing Options                                                                      |     |

| 40 | Serial RapidIO (SRIO) Registers                                                                          |     |

| 41 | Peripheral ID Register (PID) Field Descriptions                                                          |     |

| 42 | Peripheral Control Register (PCR) Field Descriptions                                                     |     |

| 43 | Peripheral Settings Control Register (PER_SET_CNTL) Field Descriptions                                   |     |

| 44 | Peripheral Global Enable Register (GBL_EN) Field Descriptions                                            |     |

| 45 | Peripheral Global Enable Status Register (GBL_EN_STAT) Field Descriptions                                |     |

| 46 | Block <i>n</i> Enable Registers and the Associated Blocks                                                |     |

| 47 | Block <i>n</i> Enable Register (BLK <i>n</i> _EN) Field Descriptions                                     |     |

| 48 | Block <i>n</i> Enable Status Registers and the Associated Blocks                                         |     |

| 49 | Block <i>n</i> Enable Status Register (BLK <i>n</i> _EN_STAT) Field Descriptions                         | 120 |

| 50                                                                                                 | RapidIO DEVICEID1 Register (DEVICEID_REG1) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 121                                                                                                                 |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 50<br>51                                                                                           | RapidIO DEVICEID2 Register (DEVICEID_REG2) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| 52                                                                                                 | PF_16B_CNTL Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| 53                                                                                                 | Packet Forwarding Register <i>n</i> for 16-Bit DeviceIDs (PF_16B_CNTL <i>n</i> ) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                     |

| 53<br>54                                                                                           | PF_8B_CNTL Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

|                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                     |

| 55                                                                                                 | Packet Forwarding Register <i>n</i> for 8-Bit DeviceIDs (PF_8B_CNTL <i>n</i> ) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

| 56                                                                                                 | SERDES_CFGRX <i>n</i> _CNTL Registers and the Associated Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

| 57                                                                                                 | SERDES Receive Channel Configuration Register <i>n</i> (SERDES_CFGRX <i>n</i> _CNTL) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| 58                                                                                                 | EQ Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| 59                                                                                                 | SERDES_CFGTXn_CNTL Registers and the Associated Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| 60                                                                                                 | SERDES Transmit Channel Configuration Register <i>n</i> (SERDES_CFGTX <i>n</i> _CNTL) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |

| 61                                                                                                 | DE Bits of SERDES_CFGTXn_CNTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| 62                                                                                                 | SWING Bits of SERDES_CFGTXn_CNTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     |

| 63                                                                                                 | SERDES_CFGn_CNTL Registers and the Associated Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 130                                                                                                                 |

| 64                                                                                                 | SERDES Macro Configuration Register <i>n</i> (SERDES_CFG <i>n</i> _CNTL) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 130                                                                                                                 |

| 65                                                                                                 | DOORBELLn_ICSR Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132                                                                                                                 |

| 66                                                                                                 | DOORBELLn Interrupt Condition Status Register (DOORBELLn_ICSR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 132                                                                                                                 |

| 67                                                                                                 | DOORBELLn_ICCR Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 133                                                                                                                 |

| 68                                                                                                 | DOORBELL <i>n</i> Interrupt Condition Clear Register (DOORBELL <i>n</i> _ICCR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 133                                                                                                                 |

| 69                                                                                                 | RX CPPI Interrupt Condition Status Register (RX_CPPI_ICSR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| 70                                                                                                 | RX CPPI Interrupt Condition Clear Register (RX_CPPI_ICCR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

| 71                                                                                                 | TX CPPI Interrupt Condition Status Register (TX_CPPI_ICSR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| 72                                                                                                 | TX CPPI Interrupt Condition Clear Register (TX_CPPI_ICCR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

| 73                                                                                                 | LSU Interrupt Condition Status Register (LSU_ICSR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| 74                                                                                                 | LSU Interrupt Condition Clear Register (LSU_ICCR) Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

| 75                                                                                                 | Error, Reset, and Special Event Interrupt Condition Status Register (ERR_RST_EVNT_ICSR) Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |

| 10                                                                                                 | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 142                                                                                                                 |

| 76                                                                                                 | Error, Reset, and Special Event Interrupt Condition Clear Register (ERR_RST_EVNT_ICCR) Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

|                                                                                                    | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 143                                                                                                                 |

| 77                                                                                                 | DOORBELLn_ICRR Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 144                                                                                                                 |

| 78                                                                                                 | DOORBELLn Interrupt Condition Routing Register Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144                                                                                                                 |

|                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                     |

| 79                                                                                                 | RX CPPI Interrupt Condition Routing Register Field Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 145                                                                                                                 |